LC3 Registers

08 Jun 2020In order to supplement our understanding of LC3 datapath, we dive into Register File in finer details

The 8 LC3 General Purpose Registers live inside the Register File Circuit. They are small, fast memory with 16-bit addressability per register.

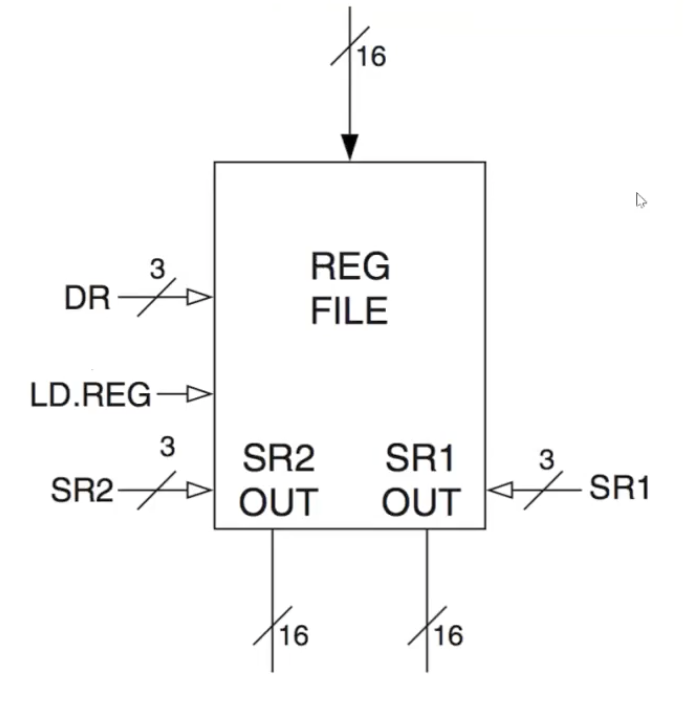

Figure 1 shows the Register File Circuit.

Input

The Reg File is a dual-ported memory, which means that it can read 2 registers at a time–the SR1 (3-bit address) and SR2 (3-bit address).

Output

Recall an advantage of the Leader-Follower Flip Flop that is used to build registers–you can simultaneously read your next value as you write the current value. With LC3 File Reg, you can simulataneously read two register values as you write one register value in a single clock cycle.